Stm32contacts流程一般来说有三种形式:一类是如前所述JTAG(SWD)的流程浏览形式,此种形式需要虚拟环境才能高效率与方便快捷地增容STM32电脑掌控系统掌控系统,比如,J-LINK与U-LINK等均是较好的虚拟环境,此种形式的益处是能够新浪网增容,直接用源码浏览。

另外一类如前所述串行的流程浏览形式,STM32本款均支持此种形式,此种形式一般来说通过两个USB线和适当的ISP浏览应用软件就能将HEX文档浏览到STM32晶片,这种有位益处是不能曝露源码,就行了找对个人教呵呵就能去操作方式,比如说去顾客当晚升级换代标识符等。

上面他们重点如是说呵呵此种形式是怎么同时实现的:

每一STM32晶片上都有三个插口BOOT0和BOOT1,这三个插口在晶片登位时的阻抗决定了登位后从那个地区已经开始执行流程:

(1)BOOT1=x,BOOT0=0,从采用者的SSD(Flash)开启,这是恒定的工作商业模式;

(2)BOOT1=0,BOOT0=1,从掌控系统存贮开启,此种开启的形式有原装增设的两个ROM,这个地区专门针对增设了几段BootLoader,就是一般来说说的ISP流程,采用者无法抹除和修正。

(3)BOOT1=1,BOOT0=1,从内建的SRAM开启,此种商业模式能用于增容,一般来说不能采用此种商业模式开启,因为过载后SARM数据会遗失,一般来说只在增容时采用。

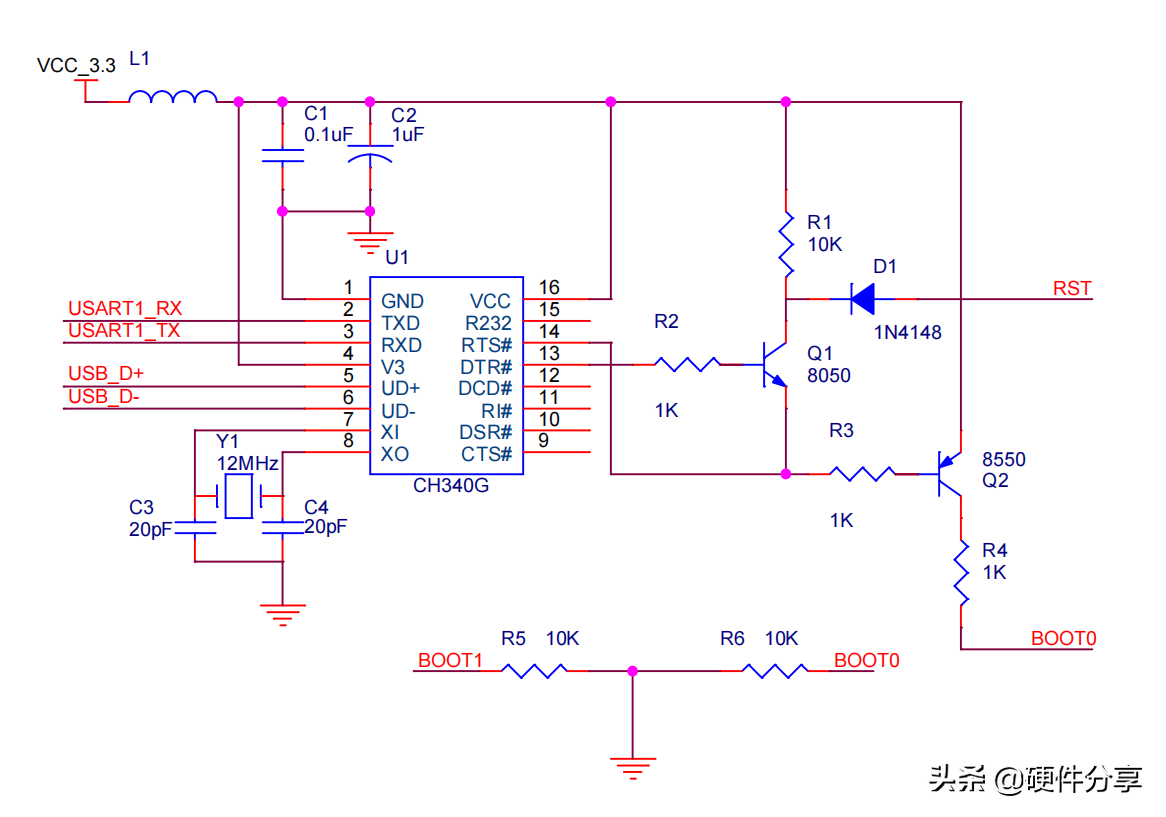

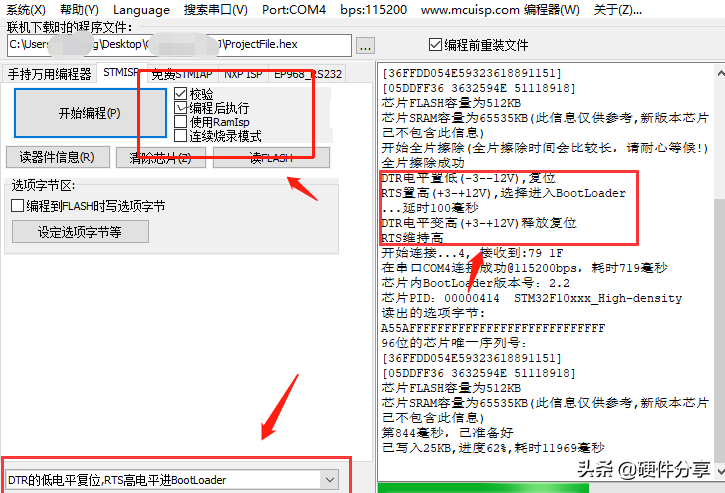

上面进行设计图分析,此电阻只能相连串行1。BOOT1一般来说预设为低阻抗,在电阻上电后RTS、DTR为低阻抗,在用contacts应用软件时,他们在应用软件上方选择DTR的低阻抗登位,RTS低阻抗进BootLoader。

电阻中Q2为pnp真空管,RTS输入低阻抗时,偏压,BOOT0才为低阻抗;

电阻中Q1为npn真空管,DTR输入低阻抗时,偏压,RST才为低阻抗;

首先,contacts应用软件掌控DTR插口输入高,RTS插口输入低,这种Q2偏压了,BOOT0被抬高,即同时实现增设BOOT0为1,同时Q1也会偏压,STM32的登位脚被拉低,同时实现登位。

然后,延迟时间100ms后,contacts应用软件掌控DTR插口输入低阻抗,RTS插口继续为低阻抗,这时STM32的登位插口,由于Q1无须偏压,转变成低阻抗,STM32结束登位,但是BOOT0还是保持为1,从而进入ISP商业模式,接著contacts应用软件就能已经开始相连STM32,浏览标识符了,ISP浏览完后,手动登位运转。

设计图

浏览应用软件

2.分享目的仅供大家学习和交流,您必须在下载后24小时内删除!

3.不得使用于非法商业用途,不得违反国家法律。否则后果自负!

4.本站提供的源码、模板、插件等其他资源,都不包含技术服务请大家谅解!

5.如有链接无法下载或失效,请联系管理员处理!

6.本站资源售价只是赞助,收取费用仅维持本站的日常运营所需!